## The 6809 microprocessor looks like reviving interest in the \$50 bus. We take a look at its various virtues.

The \$100 bus standard has become so accepted by the microcomputer community that other bus standards have tended to be ignored. The \$100, with so many manufacturers supporting so many different computers and plug-in cards, has tended to kill off any attempts at alternatives. Perhaps the one exception has been the similarly named \$50 bus. In the same way that the \$100 came from the control line requirements of the Intel 8080, the \$50 came from the Motorola 6800. Most of the similarities and differences between the two buses can be seen in Table 1.

#### Micro History

In the early days of microcomputing the S50 bus was almost as popular as the \$100. Indeed, in this country, there was a time when the \$50 was by far the most used, mainly due to the pioneering efforts of Computer Workshop importing SWTP equipment. Later the \$100 became the most popular bus, for various reasons many different manufacturers produced equipment based on the \$100. The Z80 was the most powerful MPU and was only available on the \$100 (a brief experiment using the Z80 on the S50 did not catch on). Microsoft produced a range of powerful software for the 8080/Z80, and eventually Digital Research produced CP/M, a rapidly accepted disc operating system.

My own route into microcomputers was via the \$50/6800 system and, like many others, I eventually believed that the \$100 was better and switched to an \$100/Z80 based system. After some time

S50 NAME

pins 1 to 50)

D1

D2

D3

using CP M, interfacing various bits and pieces of equipment and trying hard to believe what everyone else was still telling me about \$100/Z80 systems, I decided to give the \$50 another try. My reasons for abandoning the overcomplex hardly standard \$100, the arbitrary architecture of the Z80, and the primitive CP/M, will become clearer during the rest of this article.

#### S50 Revisited

The basic structure of the S50 bus can be seen in Table 2. Nearly all of the

| Produced By                                           | S100<br>ALTAIR             | \$50<br>South West Tech.                                     |

|-------------------------------------------------------|----------------------------|--------------------------------------------------------------|

| 1st CPU                                               | 8080                       | Products (SWTP)<br>6800                                      |

| 2nd CPU<br>Other CPUs                                 | Z80<br>8085                | 6809<br>6502 / 280<br>Inct popular)                          |

| 1/0                                                   | 256 undecoded              | 8 fully decoded<br>4 16 registers each                       |

| Improvements<br>Manufacturers<br>Main DOS<br>Software | Many<br>CP/M<br>wide range | S50C<br>Few large companies<br>FLEX<br>nor much applications |

Table 1. Similarities and differences between \$100 and \$50 users.

| D6<br>D7<br>A15                                                 |                                                                                            |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| 10                                                              | 16 address lines                                                                           |

| AO<br>GRD<br>GRD<br>GRD<br>+ BV<br>+ BV                         | Ground                                                                                     |

| + 8V<br>- 16V<br>+ 16V<br>not used<br>MRST<br>NMI<br>IRQ<br>UD2 | Location (index) pin<br>Manual Reset<br>Non Masable Interrupt<br>Interrupt<br>User defined |

| UD1<br>92<br>VMA<br>R/W<br>Reset                                | User defined<br>Phase two clock (1-2 MHz)<br>Valid address indication<br>Read/Write        |

| BA<br>Ø1                                                        | Bus available<br>Phase one clock                                                           |

| HALT<br>110b<br>150b<br>300b<br>600b<br>1200b                   | 110 baud line<br>150 baud line<br>300 baud line<br>600 baud line<br>1200 baud line         |

DESCRIPTION

eight bi-directional

inverted

data lines

Table 2. The \$50 bus structure

**BOARD THE S50**

bus lines are derived from the 6800 MPU's connections. 16 address lines provide the same amount of addressing as the \$100. Eight bi-directional data lines contrast with the \$100's 16 unidirectional data lines. Most of the other lines are fairly straightforward and self-explanatory. Anyone familiar with the \$100 will be surprised at the relatively few control lines used. That they are enough is something that can only be proved by experience.

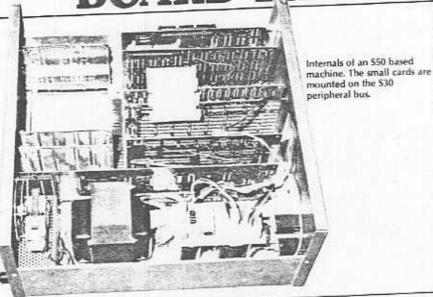

The greatest difference between the 550 and the \$100 is, in fact, not part of the main bus definition at all. The S50 bus has an auxiliary I/O bus consisting of 30 pins (not strictly a bus at all because not all the pins are paralleled). This is sometimes referred to as the \$30 bus and its specifications can be seen in Table 3. The most unusual feature of the \$30 bus is the presence of pin 1, an I/O select pin. The 550 bus is so organised that every 530 bus slot occupies a certain number of address locations (usually four, but see the definition of the S50C later) and when an address in the slot's range is output on the main bus the I/O select pin goes low. This means that any I/O card plugged into an \$30 slot need only examine pin 1 to discover if it is being addressed or not. Thus, I/O cards need very little circuitry for this purpose.

Although not part of the S50 standard, most S50 computers have eight S30 I/O ports, usually at the rear of the main chassis. As the S50 bus is organised around the 6800 MPU the S30 I/O bus is organised around the 6800 PIA, and the 6850 ACIA. Thus RS0 and RS1 are used as register select lines to determine which control/data register of a 6820 is being addressed. Having only two register selects means that each S30 slot can only access four I/O registers. Thus, more advanced peripheral chips, such as the MOSTEK 6522 VIA, cannot be used. (A

problem overcome with the advent of the S50C extended but — see later). To recap, each S30 slot has one I O select pin which goes low when the slot is addressed and occupies four distinct addresses in the main memory space, usually referred to as an I O port.

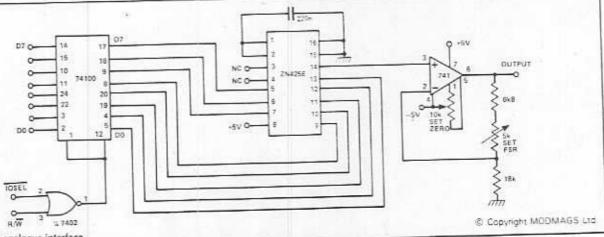

### A Simple Interface

To show how easy it is to construct a custom interface on the \$50 bus we will consider a simple example. Rather than choosing to interface a standard Motorola device such as a 6820 PIA, which, after all the \$30 bus was designed to make easy, we will interface the ZN425E D to A converter chip.

The ZN425E chip is not designed to be used directly on a microprocessor bus and has only eight non-latched data inputs. So, the first thing we must do is to provide a latch. A 74100 octal latch solves this problem nicely and as we are not too fussy about decoding all of the register locations, a 7402 NOR gate

| S30 NAME                               | DESCRIPTION                               |

|----------------------------------------|-------------------------------------------|

| (pins 1 to 30)<br>UD3<br>UD4<br>- 12V  | user defined<br>user defined              |

| + 12V<br>GND<br>GND<br>not used<br>NMI | Location (index) pin                      |

| RS0<br>RS1<br>D0                       | Register select 0<br>Register select 1    |

| D1<br>D2<br>D3<br>D4<br>D5<br>D6       | eight bit<br>bi-directional<br>data lines |

| D7<br>2/2<br>R/W<br>+8V                | Phase two clock                           |

| - 8V<br>1200b<br>600b<br>300b          |                                           |

| 150b<br>110b<br>RESET<br>I/O SELECT    |                                           |

Table 3. The \$30 bus structure.

A close-up of the \$30/\$50 buses. Note the neat way the cards mount directly to the rear of the case allowing sockets to be easily fitted.

| OLD S50 NAM                                              | ME NEW SEC                                    | COMMENTS                                                                |

|----------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------|

| MRST                                                     | MRDY                                          | Memory ready line (for slow                                             |

| NMI<br>UD2                                               | BUSY                                          | memory) Bus in use Fast interrupt request (New 6809                     |

| UD1<br>02<br>01<br>110b<br>150b<br>300b<br>600b<br>1200b | 0<br>E<br>BS<br>BUSRO<br>S3<br>S2<br>S1<br>S0 | interrupt) Clock line Clock line Bus status Bus request A19 A18 A17 A16 |

Table 4. Changes on the \$50C.

| LD 530 NA                         | ME NEW S30C                          | COMMENTS                                                                         |

|-----------------------------------|--------------------------------------|----------------------------------------------------------------------------------|

| UD3<br>UD4<br>NMI<br>600b<br>150b | RS2<br>RS3<br>FIRO<br>4800b<br>9600b | Register select line two<br>Register select line three<br>Fast interrupt request |

Table 5. Changes on the \$30C.

solves the problem of when to latch the data bus. The final circuit (including analogue components) can be seen in Fig. 1. It's as easy as that!

### The Processors — 6800 And 6809

Another delight of the S50 bus is the 6800 microprocessor. The standard micro on the S50 may only have two accumulators (A and B registers), one index register (X), and a stack pointer, but its addressing modes are extensive and uniform. That is, every instruction (except for a few obvious exceptions) may use all of the addressing modes. All in all, the 6800 is a well designed processor that is easy to program in assembler code.

Recently Motorola has introduced the 6809 as a replacement for the 6800. With two accumulators, index registers and stack pointers, the 6809 is powerful. Its addressing modes include all of the 6800's plus many more. I would urge anyone considering a new processor to study the 6809 carefully rather than simply choosing a "standard" Z80. From the point of view of students and teachers the 6809 provides a good model of a well designed MPU - simple, elegant and complete. From the point of view of anyone considering real-time processing the 6809 is roughly one and a half times faster than a Z80 and a double speed version will be available soon Clearly the 6809 will be with us for some time

#### Extended Addressing

With the 6809 came the need to in-

crease the addressing range of the S50 bus. Also some extra control lines used by the 6809 are not included in the S50 bus definition. These problems have been overcome by the \$50C bus definition, the main features of which can be seen in Table 4, the corresponding new \$30C bus definition is given in Table 5. The main improvements are the provision of four extra address lines, giving access to one megabyte of main memory, and two extra register select lines, giving each I O port sixteen memory locations. These two details make the S50C bus ready for the next generation of micros. Comparing the S50C with the S50 definition indicates that \$50/\$30 devices will work on the \$50C \$30C bus with little or no modification. Going the other way is not always so easy but some manufacturers make plug-in cards that can be used on both versions of the \$50.

#### Software

Although most of this article has been about hardware characteristics of the \$50 \$50C bus, it would not be complete without a few words about software. In particular the most used operating system, FLEX, deserves a word of praise So much has been written about CP M and so little about FLEX that it would take a complete feature (or more) to describe the advantages that FLEX has over CP.M. From assembly language disc files can be created. renamed etc. with very little effort. FLEX is well documented and has a range of programming utilities (such as DEBUG, a 6800 6809 simulator). High level

languages are also available and share most of FLEX's features. It is enough (for the moment) to say that all the software making up the FLEX system is user, rather than programmer, oriented.

#### The Future

At this point I hope I have convinced you that the \$50 bus has advantages for some purposes. I would not suggest that the \$50 was always the best — it too has its problems. In particular for the next generation of micros an eight bit bidirectional data bus will be too small. Whether another eight pins (or more) can be found is a matter of some doubt but, even so, a 68000 card for the 550 is scheduled for early this year. It is certainly true that the deficencies will become more apparent as time moves on but the \$50 will always be a simple-to-use, and cheap, alternative to whatever else comes along

With the introduction of the 6809, the S50 bus is becoming popular again and a great deal of new activity and interest is evident (viz 68' MICRO JOURNAL). Also, the advent of so many non-S100 bus machines, such as PET, Apple etc, means that the S50 stands a good chance of being used as much as, if not more than, the S100 in future.

The real strength of a bus standard that will endure for the future comes from the number of cards available and planned that can be used on it. To show that the \$50 is healthy I include Table 6 — a list of \$50 cards that I know about along with their availability. This list is by no means complete and I apologise to

### BOARD THE S50

any manufacturers whose products I may have omitted.

#### Conclusion

By this time it should be clear that I think the \$50 bus plus the 6809 plus FLEX makes a good system. In particular:

- \*S50 cards are simple and cheap

- \*The S30 bus is easy to interface to a variety of devices

- \*A wide range of cards is inproduction

- \*A wide range of cards is planned for the future by a number of manufacturers

- \*The 6089 is an elegant and powerful processor

- \*FLEX is an elegant and powerful operating system

- \*Some excellent systems software is available (BASIC, Pascal, FORTRAN etc)

| CARD                              | COMMENTS                                                                                | AVAILABILITY             |

|-----------------------------------|-----------------------------------------------------------------------------------------|--------------------------|

| 6800 CPU<br>6800 CPU<br>68000 CPU | At least three types<br>Two current more clanned<br>Not much information yet            | NOW<br>NOW<br>1st Q 1981 |

| Memory                            | All types from 4K to 30K with many                                                      |                          |

| SERIAL<br>PARALLEL                | different features<br>One, two or eight channel RS232<br>One or eight (20 bit) channels | NOW<br>NOW<br>NOW        |

| TIMERS                            | Interrupt and interval                                                                  | NOW                      |

| EPROM PRG<br>EPROM CARD           |                                                                                         | NOW<br>NOW               |

| A to D's<br>D to A's              | Fast 12 and 8 bit types<br>Fast 12 and 8 bit types                                      | NOW<br>NOW               |

| VDU CARD                          | With low resignaphics                                                                   | NOW                      |

| HIGH RES                          | High resolution graphics card                                                           | 3rd Q 1980               |

| DISC CONTRO<br>DISC CONTRO        | L With drives for both 8" and 5"<br>L Without drives for 8" and 5"                      | NOW<br>3rd Q 1980        |

| PROTOTYPE                         |                                                                                         | NOW<br>NOW               |

A pair or Noical 550 based cards showing their compactness.

Our thanks are due to Computer Workshop of 38 Dover Street, London for providing photographic facilities.

# MICHEPAUSES INS

# AN INTRODUCTION FOR THE PROFESSIONAL LAYMAN

by Paul Kimberley B.Sc., C.Eng., M.I.Prod. Eng.

## CAN YOUR BUSINESS AFFORD TO BE WITHOUT IT?

This book provides the much needed introduction to the principles and jargon involved in the modern microelectronic and computer systems that can and will rapidly transform business and industry. If the microelectronic revolution isn't going to pass you by, here's all you need to know about:

- The principles of the computer and the development of the related technology over the past 30 years

- Current market trends and the ever-widening range of applications

- Microelectronics: the components that make up a modern microprocessor

- Practical applications: two case studies, one industrial, one administrative, which provide a step-by-step guide to applying the technology

- Additional hardware surrounding the microprocessor

- Glossary: over 1000 of the most commonly used terms in the world of microelectronics

Planned as a businessman's self-defence kit against the secret language of the technocrats, this is a book that every manager needs

Please supply.... copies of MICROPROCESSORS by Paul Kimberley at £7.95 plus 85p. postage and packing (overseas orders: allow £1.20 p & p). I enclose a cheque payable to Hayes Kennedy Ltd. for £... NAME:

ADDRESS:

Hayes Kennedy Ltd, 103 High Street, Thame,

Oxfordshire 0X9 3DZ Please allow 28 days for delivery.

Also obtainable from your local bookseller.