## WESTERN DIGITAL

# WD2123 DEUCE Dual Enhanced Universal Communications Element

#### **FEATURES**

- TWO INDEPENDENT ASYNCHRONOUS FULL DUPLEX DATA COMMUNICATION CHANNELS (2 BOARTS)

- TWO INDEPENDENT BAUD RATE GENERATORS (ONE PER CHANNEL)

- EACH CHANNEL WITH FOLLOWING FEATURES:

- SELECTABLE 5 TO 8 BIT CHARACTERS

- 1X, 16X, 64X CLOCK RATES

- 16 SELECTABLE BAUD RATE CLOCK FREQUENCIES (INTERNAL)

- LINE BREAK DETECTION AND GENERATION

- 1, 1½, OR 2 STOP BIT SELECTION

- FALSE START BIT DETECTION

- ODD OR EVEN PARITY GENERATE AND DETECTION

- OVERRUN AND FRAMING DETECTION

- DOUBLE BUFFERING OF DATA

- TTL COMPATIBLE INPUTS AND OUTPUTS

- COMPATIBLE WITH 8251A (ASYNC ONLY) AND WD1983 DEVICES

- DIAGNOSTIC LOCAL LOOP-BACK MODE

- RXD INITIALIZATION UPON MASTER RESET

- ON-BOARD OSCILLATOR FOR EASE OF USE WITH A CRYSTAL

- VERSATILE CLOCK SELECT OPTIONS FOR INDEPEN-DENT TRANSMIT AND RECEIVE RATES

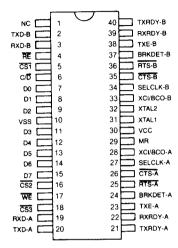

PIN DESIGNATION

#### DESCRIPTION

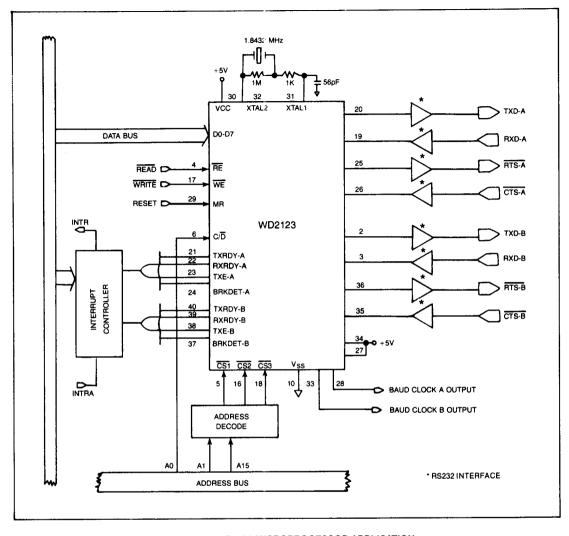

The Western Digital WD2123 Dual Enhanced Universal Communications Element (DEUCE) is a single chip MOS/LSI Data Communications Controller Circuit that contains two independent full-duplex asynchronous RECEIVER/TRANS-MITTER CHANNELS and two independent BAUD RATE GENERATORS. The WD2123 is fabricated in N-Channel silicon gate technology and is packaged in a 40 pin plastic or ceramic package. All inputs and outputs are TTL compatible.

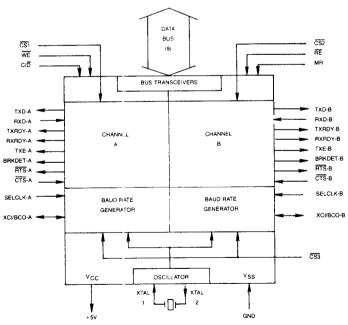

The WD2123 Block Diagram is shown in Figure 1. The WD2123 is a merger of two WD1983s and one WD1941 from WDC's line of communications devices on one piece of silicon. The 1983 is an asynchronous only version of the 8251A and the 1941 is a baud rate generator. In this manner, 8251A compatibility is maintained with the WD2123 with the added features of 2 channels and 2 baud rate generators on a single chip.

As depicted from the block diagram, the channels are referred to as CHANNELS A and B. CHANNEL A, which is an asynchronous 8251A, is addressed or controlled by the input signal CS1. CHANNEL B is similarly controlled by CS2. Finally, the BAUD RATE GENERATORS are controlled by CS3.

Each channel of the WD2123 can be programmed to receive and transmit asynchronous serial data. The WD2123 per-

forms serial-to-parallel conversion on data characters received from an input/output device or a MODEM, and parallel-to-serial conversion on data characters received from the CPU. The CPU can read the status of either channel at any time. Status information on a per channel basis reported includes the type and the condition of the transfer operations being performed by the WD2123 as well as any transmission error conditions (parity, overrun, or framing). Programming the WD2123 is identical to the 8251A in the asynchronous mode, remembering that  $\overline{\text{CS1}}$ , when low, selects CHANNEL A and when  $\overline{\text{CS2}}$  is low, selects CHANNEL B.

The WD2123 BAUD RATE GENERATORS may be selected either internally or externally. The clock select logic includes a clock select control bit CR1 (CS) in each COMMAND INSTRUCTION REGISTER. This control bit allows selection of the internal baud clock or an externally applied clock and works in conjunction with the select clock pin, "SELCLK" and the external clock input/baud clock output pin, "XCI/BCO". When CS is logic 1, the external clock select mode is selected. This means that the transmit and receive clocks (TXC and RXC) are internally tied together and the select clock pin, SELCLK, will determine whether those clocks are driven from the internal baud rate generator (SELCLK is high) or from the external clock input pin, "XCI/BCO", (SELCLK is low).

#### PIN DESCRIPTION

| PIN<br>NUMBER                             | SIGNAL<br>MNEMONIC                     | SIGNAL NAME                                              | FUNCTION                                                                                                                                                                                             |

|-------------------------------------------|----------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10                                        | VSS                                    | GROUND                                                   | Ground                                                                                                                                                                                               |

| 30                                        | vcc                                    | POWER SUPPLY                                             | +5VDC power supply input.                                                                                                                                                                            |

| 7<br>8<br>9<br>11<br>12<br>13<br>14<br>15 | D0<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6 | DATA BUS                                                 | This is the 8 bit Bidirectional Data Bus. It is the means of communication between the WD2123 and the CPU. Data, control, mode and status registers are accessed via this bus.                       |

| 5                                         | ĈS1                                    | CHIP SELECT ONE                                          | V <sub>IL</sub> on this input selects Channel A and enables computer communications with Channel A Data, control and status registers.                                                               |

| 16                                        | CS2                                    | CHIP SELECT TWO                                          | V <sub>IL</sub> on this input selects Channel B and enables computer communications with Channel B Data, control and status registers.                                                               |

| 18                                        | CS3                                    | CHIP SELECT THREE                                        | $V_{1L}$ on this input select the Baud Rate registers for programming.                                                                                                                               |

| 6                                         | C/D                                    | CONTROL or DATA<br>SELECT                                | This input is used in conjunction with the appropriate Chip Select and an active read or write operation to determine register access via the Data Bus.                                              |

| 4                                         | RE                                     | READ ENABLE                                              | $V_{1L}$ on this input allows the CPU to read data, or status information from the selected register.                                                                                                |

| 17                                        | WE                                     | WRITE ENABLE                                             | V <sub>IL</sub> on this input allows the CPU to write data or control information into the selected register.                                                                                        |

| 29                                        | MR                                     | MASTER RESET                                             | V <sub>IH</sub> on this input resets both channels to the idle state and resets the status, command, mode and Data registers.                                                                        |

| 31                                        | XTAL1                                  | CRYSTAL OSCILLATOR INPUT                                 | This is the input side of the on-chip oscillator. It can also be driven by an external clock source.                                                                                                 |

| 32                                        | XTAL2                                  | CRYSTAL OSCILLATOR<br>OUTPUT                             | This is the output side of the on-chip oscillator.                                                                                                                                                   |

| 27                                        | SELCLK-A                               | SELECT CLOCK<br>(Channel A)                              | This input is used in conjunction with the Clock Select bit (CR1) in the command register to determine the baud clock source for Channel A.                                                          |

| 34                                        | SELCLK-B                               | SELECT CLOCK<br>(Channel B)                              | This input is used in conjunction with the Clock Select bit (CR1) in the command register to determine the baud clock source for Channel B.                                                          |

| 28                                        | XCI/BCO-A                              | EXTERNAL CLOCK INPUT/BAUD CLOCK OUTPUT- (Channel A)      | This is a bidirectional port, which is used as the externally applied baud clock input or the internal baud rate generator output depending on the states of SELCLK and CR1 command bit. (Channel A) |

| 33                                        | XCI/BCO-B                              | EXTERNAL CLOCK<br>INPUT/BAUD CLOCK<br>OUTPUT-(Channel B) | This is a bidirectional port, which is used as the externally applied baud clock input or the internal baud rate generator output depending on the states of SELCLK and CR1 command bit. (Channel B) |

| 26                                        | CTS-A                                  | CLEAR-TO-SEND<br>(Channel A)                             | V <sub>IL</sub> on this input enables Channel A to transmit serial data if the Transmitter is enabled.                                                                                               |

| PIN<br>NUMBER | SIGNAL<br>MNEMONIC | SIGNAL NAME                      | FUNCTION                                                                                                                                                                                                                                                                             |

|---------------|--------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35            | CTS-B              | CLEAR-TO-SEND<br>(Channel B)     | $V_{IL}$ on this input enables Channel B to transmit serial data if the Transmitter is enabled.                                                                                                                                                                                      |

| 20            | TXD-A              | TRANSMIT DATA (Channel A)        | This is the Serial Data Output from Channel A.                                                                                                                                                                                                                                       |

| 2             | TXD-B              | TRANSMIT DATA (Channel B)        | This is the Serial Data Output from Channel B.                                                                                                                                                                                                                                       |

| 19            | RXD-A              | RECEIVE DATA<br>(Channel A)      | This is the Serial Data Input for Channel A.                                                                                                                                                                                                                                         |

| 3             | RXD-B              | RECEIVE DATA<br>(Channel B)      | This is the Serial Data Input for Channel B.                                                                                                                                                                                                                                         |

| 21            | TXRDY-A            | TRANSMITTER READY<br>(Channel A) | This output, when high (VOH), alerts the CPU that Channel A is ready to accept a new data character. The TXRDY output is automatically reset whenever a character is written into the Transmit Holding Register and can be used as an interrupt to the system. CTS must be asserted. |

| 40            | TXRDY-B            | TRANSMITTER READY<br>(Channel B) | This output, when high (VOH), alerts the CPU that Channel B is ready to accept a new data character. The TXRDY output is automatically reset whenever a character is written into the Transmit Holding Register and can be used as an interrupt to the system. CTS must be asserted. |

| 22            | RXRDY-A            | RECEIVER READY<br>(Channel A)    | This output, when high (V <sub>OH</sub> ), alerts the CPU that Channel B contains a data character that is ready to be input. This output is automatically reset whenever the new character is read from the Receive Holding Register and can be used as an interrupt to the system. |

| 39            | RXRDY-B            | RECEIVER READY<br>(Channel B)    | This output, when high (V <sub>OH</sub> ), alerts the CPU that Channel B contains a data character that is ready to be input. This output is automatically reset whenever the new character is read from the Receive Holding Register and can be used as an interrupt to the system. |

| 23            | TXE-A              | TRANSMITTER EMPTY<br>(Channel A) | This output, when high (V <sub>OH</sub> ), indicates that Channel A Transmitter has no new characters to send and is waiting in an idle state.                                                                                                                                       |

| 38            | TXE-B              | TRANSMITTER EMPTY<br>(Channel B) | This output, when high (V <sub>OH</sub> ), indicates that Channel B Transmitter has no new characters to send and is waiting in an idle state.                                                                                                                                       |

| 24            | BRKDET-A           | BREAK DETECT<br>(Channel A)      | This output, when high (V <sub>OH</sub> ), indicates that the Receiver for Channel A has detected a break condition.                                                                                                                                                                 |

| 37            | BRKDET-B           | BREAK DETECT<br>(Channel B)      | This output, when high (V <sub>OH</sub> ), indicates that the Receiver for Channel B has detected a break condition.                                                                                                                                                                 |

| 25            | RTS-A              | REQUEST-TO-SEND<br>(Channel A)   | A general purpose output that is controlled by the command register bit CR5 for Channel A.                                                                                                                                                                                           |

| 36            | RTS-B              | REQUEST-TO-SEND<br>(Channel B)   | A general purpose output that is controlled by the command register bit CR5 for Channel B.                                                                                                                                                                                           |

| 1             | NC                 |                                  | No Internal Connection.                                                                                                                                                                                                                                                              |

If the internal BRG clock is selected, (SELCLK is high) then the external clock input pin becomes a BRG clock output. Hence, the mnemonic, "XCI/BCO".

When CR1 (CS) is logic 0, then internal clock select mode is selected. The transmit clock (TXC) is driven by the internal BRG clock and the receive clock is driven by the select clock pin, (SELCLK). The XCI/BCO pin becomes the baud clock output (the same signal that is being applied to TXC).

The WD2123 also provides a local loop-back test mode of operation for each channel. This diagnostic mode is independently controlled via the LB(CR7) bit of the COMMAND REGISTER. When LB is logic 1, the channel is programmed for Local Loop-Back. In this diagnostic mode, the TXD output is set to the marking (logic "1") state; the output of the TRANSMIT REGISTER is "looped-back" into the RECEIVER REGISTER input; RTS output is held high; the CTS and RXD inputs are ignored. An additional requirement is that the TEN(CR0) command bit and the REN(CR2) be logic 1. The status and output flags operate normally.

Each channel is also provided with break character generation and detection. (A break character is defined as all zero data bits, parity bit and stop bits after a valid start bit.) For break character generation, SBRK (CR3) command bit is set to a logic 1. This causes the TXD output to be forced low (spacing) for as long as SBRK is programmed high. The break detect output and status bit (SR6) is set to logic 1, indicating that the receiver has detected a break character. The framing error flag is also set to 1 for this condition.

#### **ARCHITECTURE**

The WD2123 is an eight bit bus-oriented device. Communication between the controlling CPU and the two RECEIVER/TRANSMITTER CHANNELS or the two BAUD RATE GENERATORS occurs via the 8-bit data bus through a common set of bus transceivers. Figure 1 is a Block Diagram of the WD2123.

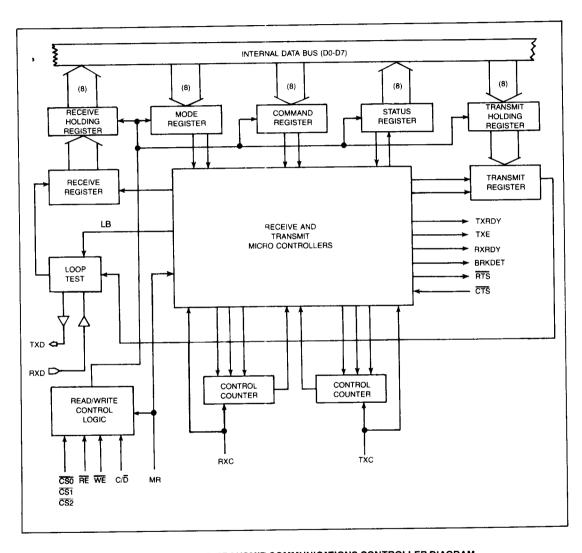

A diagram of one of the two communication controllers is shown in Figure 2. There are two accessible data registers, which buffers transmit and receive data. They are the TRANSMIT HOLDING REGISTER and the RECEIVE HOLDING REGISTER. There is a parallel-to-serial shift register, the TRANSMIT REGISTER and a serial-to-parallel shift register, the RECEIVE REGISTER.

Operational Control and monitoring of the CHANNEL is performed by two CONTROL REGISTERS (the COMMAND INSTRUCTION REGISTER and the MODE INSTRUCTION REGISTER) and the STATUS REGISTER.

A read/write control circuit allows programming/monitoring or loading/reading of data in the CONTROL, STATUS and HOLDING REGISTERS by activating the appropriate control lines: Chip Select  $(\overline{CS1}, \overline{CS2}, \overline{CS3})$ , READ ENABLE  $(\overline{RE})$ , WRITE ENABLE  $(\overline{WE})$  and CONTROL or DATA SELECT  $(C/\overline{D})$ .

Internal control of each channel is by means of two internal microcontrollers: one for transmit and one for receive. The control registers, various counters and external signals provide inputs to the microcontrollers, which generate the necessary control signals to send and receive serial data according to the programmed protocol.

FIGURE 1. WD2123 BLOCK DIAGRAM

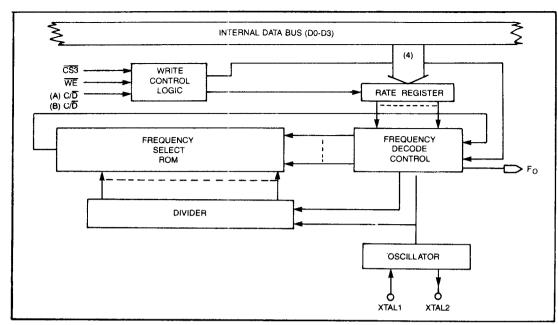

A diagram of one of the two BAUD RATE GENERATORS is shown in Figure 3. The 4 low order DATA BUS bits, D0-D3, are used to program the desired rate by loading the RATE REGISTER. Control signals CS3, We and C/D are used to select and load the appropriate register.

The contents of the RATE REGISTER is decoded and addresses a FREQUENCY SELECT ROM for the proper frequency, which is generated by the DIVIDER circuitry and the control logic.

FIGURE 2. RECEIVE/TRANSMIT COMMUNICATIONS CONTROLLER DIAGRAM

FIGURE 3. WD2123 BAUD RATE GENERATOR DIAGRAM

The WD2123 registers are addressed by the following table:

| C/D | RE | WE | CS1 | CS2 | CS3 | REGISTER SELECTED               |   |     |

|-----|----|----|-----|-----|-----|---------------------------------|---|-----|

| L   | L  | Н  | L   | Н   | Н   | RECEIVE HOLDING REG.            | _ | CHA |

| L   | н  | L  | L   | н   | н   | TRANSMIT HOLDING REG.           | _ | CHA |

| Н   | L  | н  | L   | н   | н   | STATUS REG.                     | _ | CHA |

| н   | н  | L  | L   | Н   | н   | MODE AND COMMAND REG.           | _ | CHA |

| L   | Ĺ  | н  | н   | L   | н   | RECEIVE HOLDING REG.            | _ | СНВ |

| L   | Н  | L  | н   | L   | н   | TRANSMIT HOLDING REG.           | _ | СНВ |

| н   | L  | н  | н   | L   | н   | STATUS REG.                     | _ | СНВ |

| Н   | Н  | L  | Н   | L   | н   | MODE and COMMAND REG.           | _ | СНВ |

| L   | Н  | L  | н   | н   | L   | RATE REG.                       | _ | CHA |

| н   | н  | L  | н   | Н   | L   | RATE REG.                       |   | СНВ |

| x   | x  | x  | н   | н   | н   | DATA BUS IN HIGH IMPEDANCE MODE |   |     |

#### Note:

- "L" means  $V_{IL}$  at pins. "H" means  $V_{IH}$  at pins.

- "X" means don't care.

TABLE 1. WD2123 REGISTER ADDRESSING

The WD2123 contains two MODE REGISTERS—one for each channel. The format and definition of the MODE REGISTERS are shown below:

The WD2123 contains two COMMAND REGISTERS—one per channel. The format and definition of the COMMAND REGISTERS are shown below:

| MR7 | MR6 | MR5 | MR4 | MR3 | MR2 | MR1 | MR0 |

|-----|-----|-----|-----|-----|-----|-----|-----|

| S2  | S1  | EΡ  | PEN | L2  | L1  | B2  | B1  |

| CR7 | CR6 | CR5 | CR4 | CR3 | CR2 | CR1 | CR0 |  |

|-----|-----|-----|-----|-----|-----|-----|-----|--|

| LB  | IR  | RTS | ER  | SBK | REN | cs  | TEN |  |

| B2  | B1 | BAUD RATE FACTOR                      |

|-----|----|---------------------------------------|

|     |    |                                       |

| 0   | 0  | Undefined                             |

| 0   | 1  | 1X                                    |

| 1   | 0  | 16X                                   |

| 1   | 1  | 64X                                   |

| L2  | L1 | CHARACTER LENGTH                      |

|     |    |                                       |

| 0   | 0  | 5 Bits                                |

| 0   | 1  | 6 Bits                                |

| 1   | 0  | 7 Bits                                |

| 1   | 1  | 8 Bits                                |

|     |    |                                       |

| PEN |    | PARITY ENABLE                         |

|     |    |                                       |

| 0   |    | Disable Parity                        |

| 1   |    | Enable Parity                         |

|     |    |                                       |

| EP  |    | PARITY SELECT                         |

|     |    |                                       |

| 0   |    | Odd Parity                            |

| 1   |    | Even Parity                           |

|     |    |                                       |

| S2  | S1 | NUMBER OF STOP BITS                   |

|     |    |                                       |

| 0   | 0  | Invalid                               |

| 0   | 1  | 1 Bit                                 |

| 1   | 0  | 11/2 Bits *                           |

| 1   | 1  | 2 Bits                                |

| L   |    | · · · · · · · · · · · · · · · · · · · |

TABLE 2. WD2123 MODE REGISTERS

| TEN      | TRANSMIT ENABLE                               |

|----------|-----------------------------------------------|

| 1<br>0   | Enable<br>Disable                             |

|          |                                               |

| cs       | CLOCK SELECT                                  |

|          | XMIT and RCV Clock source                     |

| 1        | common  XMIT and RCV Clock sources            |

| 0        | different                                     |

| REN      | RECEIVE ENABLE                                |

|          |                                               |

| 1        | Enable                                        |

| 0        | Disable                                       |

| SBK      | SEND BREAK CHARACTER                          |

|          |                                               |

| 1        | Force TXD Low                                 |

| 0        | Normal Operation                              |

| ER       | ERROR RESET                                   |

|          |                                               |

| 1        | Reset Error Flags                             |

| 0        | No Reset                                      |

| RTS      | REQUEST TO SEND                               |

|          |                                               |

| 1        | Force RTS pin = 0 (V <sub>OL</sub> )          |

| 0        | Force $\overline{RTS}$ pin = 1 ( $V_{OH}$ )   |

| IR       | INTERNAL RESET                                |

| 1        | Next Write to Mode Register                   |

| 0        | Next Write to Command<br>Register             |

| LB       | LOOP BACK ENABLE                              |

|          | Normal Operation Medic                        |

| 0        | Normal Operation Mode<br>Local Loop-Back Mode |

| <u>'</u> | Local Loop-back Wode                          |

TABLE 3. WD2123 CONTROL REGISTERS

<sup>\* 16</sup>X and 64X only. 1X will be 2 stop bits.

The WD2123 contains two STATUS REGISTERS—one per channel. The STATUS REGISTER is a read-only register. The format and definition of the STATUS REGISTERS are shown below:

| SR7 | SR6        | SR5 | SR4 | SR3 | SR2 | SR1       | SR0       |

|-----|------------|-----|-----|-----|-----|-----------|-----------|

| CTS | BRK<br>DET | FE  | OE  | PE  | TXE | RX<br>RDY | TX<br>RDY |

| TXRDY  | TRANSMITTER READY                                                                                                                                           |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 0    | Denotes THR is empty and ready for a new character THR not empty. (Reset when THR is loaded by CPU)                                                         |

| RXRDY  | RECEIVER READY                                                                                                                                              |

| 1      | Denotes that the RHR contains a valid                                                                                                                       |

| 0      | character RHR does not contain a valid character. (Reset when the CPU reads the RHR)                                                                        |

| TXE    | TRANSMITTER EMPTY                                                                                                                                           |

| 1<br>0 | Denotes that the TR is empty Denotes that the TR is not empty                                                                                               |

| PE     | PARITY ERROR                                                                                                                                                |

| 1 0    | Denotes Parity Error No Parity Error. (Reset by ER bit of command register)                                                                                 |

| OE     | OVERRUN ERROR                                                                                                                                               |

| 1<br>0 | Denotes Overrun Error<br>No Overrun Error. (Reset by ER bit of<br>command register)                                                                         |

| FE     | FRAMING ERROR                                                                                                                                               |

| 1 0    | Denotes Framing Error<br>No Framing Error. (Reset by ER bit of<br>command register)                                                                         |

| BRKDET | BREAK DETECT                                                                                                                                                |

| 1      | Indicates that the receiver has detected a line break condition. (FE will also be set)                                                                      |

| 0      | No Break Condition detected for at least one bit time                                                                                                       |

| CTS    | CLEAR-TO-SEND                                                                                                                                               |

| 1 0    | Indicates that the $\overline{\text{CTS}}$ pin is active (V <sub>IL</sub> ) indicates that the $\overline{\text{CTS}}$ pin is not active (V <sub>IH</sub> ) |

TABLE 4. WD2123 STATUS REGISTERS

The WD2123 contains two RATE REGISTERS that are used to select 16 BAUD rates when CR1 = 1 and SELCLK = 1. The Format of the RATE REGISTERS is shown below. Note that the Receiver and the Transmitter of any channel run off the same Baud clock except when CR1 = 0, then the Transmitter runs off the Baud Clock and the Receiver runs off an externally applied signal input on the SELCLK pin.

| D7 |   | _ |   |            |            |            | D0         |

|----|---|---|---|------------|------------|------------|------------|

| х  | × | × | Х | RA3<br>RB3 | RA2<br>RB2 | RA1<br>RB1 | RA0<br>RB0 |

When C/D = 0, RA3 to RA0 are loaded. When  $C/\overline{D} = 1$ , RB3 to RB0 are loaded.

The  $C/\overline{D}$  line is used in conjunction with  $\overline{CS3}$  and  $\overline{WE}$  to program the desired BAUD rate. When  $C/\overline{D}$  is low, Channel A is selected, and when  $C/\overline{D}$  is high, Channel B is selected. The low order 4 bits of the DATA BUS are loaded into the selected rate register, and the high order 4 bits are ignored.

When the crystal frequency equals 1.8432 MHz the following baud rates may be programmed.

|    |    |    |    |         | BAUD RATE | FREQUENCY |        |         |

|----|----|----|----|---------|-----------|-----------|--------|---------|

| R3 | R2 | R1 | R0 | BRF 1X  | BRF 16X   | BRF 64X   | (KHZ)  | DIVISOR |

| 0  | 0  | 0  | 0  | 800     | 50.0      | 12.50     | 0.80   | 2304    |

| 0  | 0  | 0  | 1  | 1,200   | 75.0      | 18.75     | 1.20   | 1536    |

| 0  | 0  | 1  | 0  | 1,760   | 110.0     | 27.50     | 1.76   | 1049    |

| 0  | 0  | 1  | 1  | 2,150   | 134.5     | 33.59     | 2.15   | 855     |

| 0  | 1  | 0  | 0  | 2,400   | 150.0     | 37.50     | 2.40   | 768     |

| 0  | 1  | 0  | 1  | 3,200   | 200.0     | 50.00     | 3.20   | 576     |

| 0  | 1  | 1  | 0  | 4,800   | 300.0     | 75.00     | 4.80   | 384     |

| 0  | 1  | 1  | 1  | 9,600   | 600.0     | 150.00    | 9.60   | 192     |

| 1  | 0  | 0  | 0  | 19,200  | 1,200.0   | 300.00    | 19.20  | 96      |

| 1  | 0  | 0  | 1  | 28,800  | 1,800.0   | 450.00    | 28.80  | 64      |

| 1  | 0  | 1  | 0  | 38,400  | 2,400.0   | 600.00    | 38.40  | 48      |

| 1  | 0  | 1  | 1  | 57,600  | 3,600.0   | 900.00    | 57.60  | 32      |

| 1  | 1  | 0  | 0  | 76,800  | 4,800.0   | 1,200.00  | 76.80  | 24      |

| 1  | 1  | 0  | 1  | 115,200 | 7,200.0   | 1,800.00  | 115.20 | 16      |

| 1  | 1  | 1  | 0  | 153,600 | 9,600.0   | 2,400.00  | 153.60 | 12      |

| 1  | 1  | 1  | 1  | 307,200 | 19,200.0  | 4,800.00  | 307.20 | 6       |

TABLE 5. WD2123 BAUD RATE SELECTION

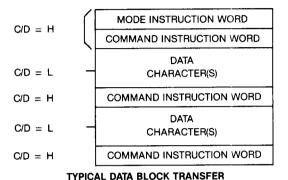

#### READ/WRITE OPERATIONS

The WD2123 must be initialized after a MASTER RESET pulse by first writing the MODE INSTRUCTION word and then the COMMAND INSTRUCTION word. Thereafter, every control write to the device is interpreted as a COMMAND word. If it is desired to re-program the MODE REGISTER, a COMMAND REGISTER bit, INTERNAL RESET (CR6), allows the next control write data to be entered into the MODE REGISTER.

#### **OPERATING DESCRIPTION**

The WD2123 is primarily designed to operate in an 8 bit microprocessor environment, although other control logic schemes are easily implemented. The DATA BUS and the interface control signals ( $\overline{CS1}$ ,  $\overline{CS2}$ ,  $\overline{CS3}$ ,  $\overline{CS3}$ ,  $\overline{CS1}$ ,  $\overline{RE}$ ,  $\overline{WE}$ ) should be connected to the microprocessor's data bus and system control bus. A 1.8432 MHz crystal should be connected to the WD2123 as shown in figure 5. The appropriate TXC (RXC) clock frequencies should be programmed via system software. Different Baud clock configurations are possible, such as separate transmit and receive frequencies, and are outlined in the general description.

For typical data communication applications, the RXD and TXD input/outputs can be connected to RS-232C interface circuits. Interface control signals, CTS and RTS, are controlled and sensed by the CPU through the COMMAND and STATUS REGISTERS and can be configured in several ways. The CTS input can be used to synchronize the transmitter to external events.

The TXRDY, RXRDY, TXE and BRKDET FLAGS may be connected to the microprocessor system as interrupt inputs or the STATUS REGISTER can be periodically read in a polled environment to support data communication control operations.

The SBRK bit of the COMMAND REGISTER (CR3) is used to send a Break Character. (A Break Character is defined as a start bit, and all zero data, parity and stop bits.) When the CR3 bit is set to a "1", it causes the transmitter output, TXD, to be forced low after the last bit of the last character is transmitted.

The Receiver is equipped with logic to look for a break character. When a break is received, the BREAK DETECT (BRKDET) FLAG and STATUS bit are set to "1". When the receiver input line goes high (V<sub>IH</sub>) for at least one clock period, the receiver resets the BRKDET FLAG and resumes its search for a start bit.

#### PROGRAMMING PROCEDURE

The programming sequence of the two channels will be different, depending on whether it is an initialization sequence (that is, one performed right after a hardware master reset occurs) or a re-programming sequence (that is, one performed to change the protocol characteristics (Parity, rate, character length, etc.) after the device has been previously operating in the system). The programming sequence differs, in that, after a master reset, the chip is set to expect the first control write operation  $(C/\overline{D}=1)$  to contain a mode instruction. Any subsequent control write operations will be transferred to the command instruction register.

Now when it is desired to change the mode instruction register contents, the following re-programming sequence should be performed. A Command Control word of "40" Hex is written to the Chip. This turns off the Receiver and Transmitter and sets the IR (Internal Reset) bit. This bit causes the read/write control logic to expect the next control write operation to be a new mode instruction. After the new mode instruction is written to the chip, all subsequent control write operations will again be interpreted as command instructions. Therefore, after the new mode instruction is performed, the next command would turn the receiver and transmitter back on and resume normal Data operations.

FIGURE 4. WD2123 MICROPROCESSOR APPLICATION

#### **ABSOLUTE MAXIMUM RATINGS**

VDD with respect to VSS

0.5V to + 12V

Voltage on Any Pin with Respect to Ground

- 0.5V to + 7V

Power Dissipation

500 Mw.

Lead Temperature (Soldering 10 sec.)

300 °C

STORAGE TEMPERATURE: Ceramic: —65°C to +150°C Plastic: —55°C to +125°C

#### **CRYSTAL SPECIFICATIONS:**

| Temperature range | <br>0°C to +70°C |

|-------------------|------------------|

| Series resistance | <br>300Ω to 500Ω |

| Overall tolerance | <br>± 0.01%      |

Note: Maximum ratings indicate limits beyond which permanent damage may occur. Continuous operation at these limits is not intended and should be limited to those conditions specified under dc electrical characteristics.

#### TABLE 6. DC ELECTRICAL CHARACTERISTICS

$T_A = 0^{\circ}C \text{ to } +70^{\circ}C; V_{CC} = 5.0V \pm 5\%; GND = 0V$

| SYMBOL          | PARAMETER                                  | MIN  | ТҮР         | MAX      | UNIT     | TEST CONDITIONS                                                |

|-----------------|--------------------------------------------|------|-------------|----------|----------|----------------------------------------------------------------|

| V <sub>IL</sub> | Input Low Voltage                          | -0.5 |             | 0.8      | ٧        |                                                                |

| VIH             | Input High Voltage                         | 2.0  |             | Vcc      | ٧        |                                                                |

| VOL             | Output Low Voltage                         |      | · · ·       | 0.45     | ٧        | l <sub>OL</sub> = 1.6 mA                                       |

| Voн             | Output High Voltage                        | 2.4  | <del></del> |          | ٧        | I <sub>OH</sub> =100 uA                                        |

| <sup>1</sup> DL | Data Bus Leakage<br>(High Impedance State) |      |             | 50<br>10 | uA<br>uA | V <sub>OUT</sub> = 0.45V<br>V <sub>OUT</sub> = V <sub>CC</sub> |

| I <sub>IL</sub> | Input Leakage                              |      |             | 10       | uА       | V <sub>IN</sub> = V <sub>CC</sub>                              |

| lcc             | Power Supply Current                       |      | 100         | 125      | mA       | V <sub>CC</sub> = 5.25V<br>No Load                             |

#### TABLE 7. CAPACITANCE

$T_A = 25$ °C;  $V_{CC} = GND = 0V$

| SYMBOL           | PARAMETER         | MIN | ТҮР | MAX | UNIT | TEST CONDITIONS                  |

|------------------|-------------------|-----|-----|-----|------|----------------------------------|

| CiN              | Input Capacitance |     |     | 10  | pF   | f <sub>C</sub> = 1MHz            |

| C <sub>I/O</sub> | I/O Capacitance   |     |     | 20  | pF   | Unmeasured pins returned to GND. |

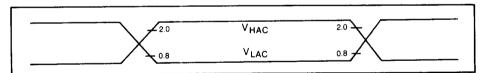

### AC ELECTRICAL CHARACTERISTICS TABLE 8. A.C. CHARACTERISTICS

$T_A = 0$ °C to + 70C;  $V_{CC} = 5.0V \pm 5$ %; GND = 0V

| SYMBOL                   | CHARACTERISTIC                                                               | MIN        | MAX        | UNITS      | CONDITIONS                                                   |

|--------------------------|------------------------------------------------------------------------------|------------|------------|------------|--------------------------------------------------------------|

| BUS PARAME<br>Read Cycle | ETERS                                                                        |            |            |            |                                                              |

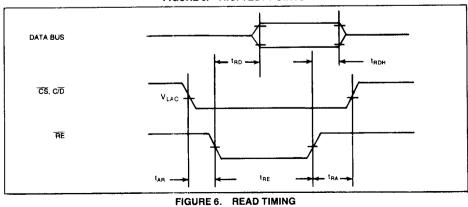

| <sup>t</sup> AR          | Address Stable Before READ ( $\overline{CS}$ ,C/ $\overline{D}$ )            | 50         |            | ns         |                                                              |

| t <sub>RA</sub>          | Address Hold Time for READ $(\overline{CS}, C/\overline{D})$                 | 50         |            | ns         |                                                              |

| †RE                      | READ Pulse Width                                                             | 230        |            | ns         |                                                              |

| t <sub>RD</sub>          | Data Delay from READ                                                         |            | 200        | ns         | C <sub>L</sub> = 50 pF                                       |

| t <sub>RDH</sub>         | READ to Data Floating                                                        | 25         | 200        | ns         | C <sub>L</sub> (Max) = 50 pF<br>C <sub>L</sub> (Min) = 15 pF |

| Write Cycle              |                                                                              |            |            |            |                                                              |

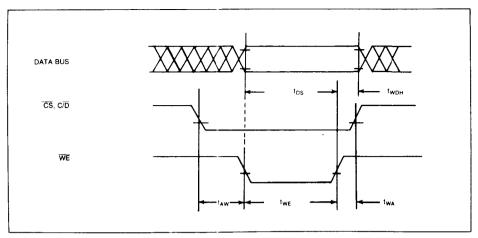

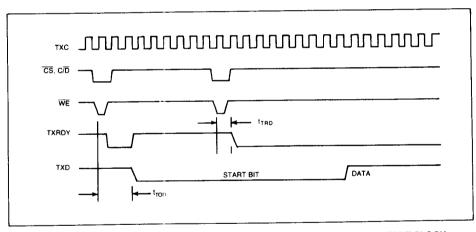

| <sup>t</sup> AW          | Address Stable Before WRITE                                                  | 50         |            | ns         |                                                              |

| twa                      | Address Hold Time for WRITE                                                  | 50         |            | ns         |                                                              |

| twe                      | WRITE Pulse Width                                                            | 230        |            | ns         |                                                              |

| t <sub>DS</sub>          | Data Set-Up Time for WRITE                                                   | TWE        |            | ns         |                                                              |

| twoн                     | Data Hold Time for WRITE                                                     | 100        |            | ns         |                                                              |

| OTHER TIMI               | NGS                                                                          |            |            |            |                                                              |

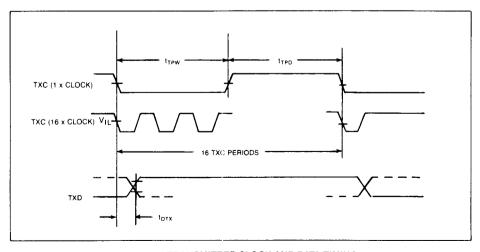

| tтхс                     | Transmit Clock Period                                                        | 1.6        |            | us         |                                                              |

| t <sub>DTX</sub>         | TxD Delay from Falling Edge of TxC                                           |            | 1000       | ns         | C <sub>L</sub> = 100 pF                                      |

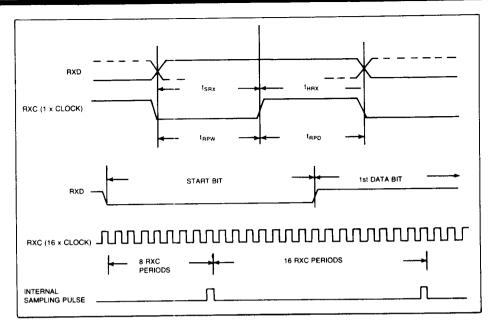

| tsax                     | Rx Data Set-Up Time to Sampling Pulse                                        | 200        |            | ns         | C <sub>L</sub> = 100 pF                                      |

| tHRX                     | Rx Data Hold Time to Sampling Pulse                                          | 200        |            | ns         | C <sub>L</sub> = 100 pF                                      |

| f <sub>TX</sub>          | Transmitter Input Clock Frequency<br>1x Baud Rate<br>16x and 64x Baud Rate   | DC<br>DC   | 500<br>600 | kHz<br>kHz | Clock<br>50% Duty<br>Cycle                                   |

| t <sub>TPW</sub>         | Transmitter Input Clock Pulse Width<br>1x Baud Rate<br>16x and 64x Baud Rate | 1.0<br>800 |            | us<br>ns   |                                                              |

| t <sub>TPD</sub>         | Transmitter Input Clock Pulse Delay<br>1x Baud Rate<br>16x and 64x Baud Rate | 1.0<br>800 |            | us<br>ns   |                                                              |

TABLE 9. A.C. CHARACTERISTICS (CONTINUED)

| SYMBC            | CHARACTERISTICS                                                           | MIN        | MAX        | UNIT             | TEST<br>CONDITION           |

|------------------|---------------------------------------------------------------------------|------------|------------|------------------|-----------------------------|

| f <sub>RX</sub>  | Receiver Input Clock Frequency<br>1x Baud Rate<br>16x and 64x Baud Rate   | DC<br>DC   | 500<br>600 | kHz<br>kHz       | Clock<br>50% Duty<br>Cycle  |

| <sup>t</sup> RPW | Receiver Input Clock Pulse Width<br>1x Baud Rate<br>16x and 64x Baud Rate | 1.0<br>800 |            | us<br>ns         |                             |

| <sup>t</sup> RPD | Receiver Input Clock Pulse Delay<br>1x Baud Rate<br>16x and 64x Baud Rate | 1.0<br>800 |            | us<br>ns         |                             |

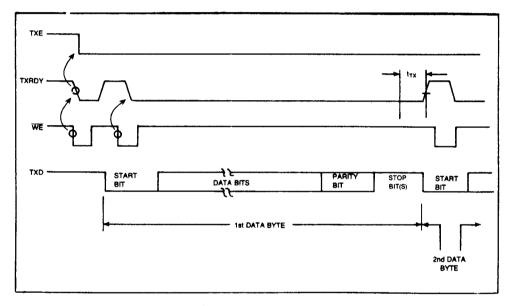

| tтх              | TxRDY Delay from Center of Stop Bit                                       |            | 8          | tRXC             | C <sub>L</sub> = 50pF (16X) |

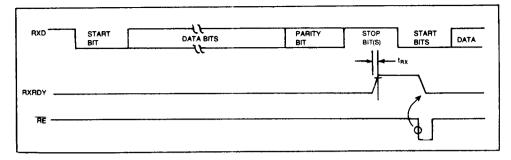

| t <sub>RX</sub>  | RxRDY Delay from Center of Stop Bit                                       |            | 1/2        | tRXC             |                             |

| tis              | Internal BRKDET Delay from Center of Data Bit                             |            | 1          | RXC              |                             |

| tTRD             | TxRDY Delay from Falling Edge of WRITE                                    |            | 450        | ns               |                             |

| <sup>t</sup> TOD | TXD Output from Falling Edge of WRITE                                     |            | 1½         | <sup>†</sup> TXC |                             |

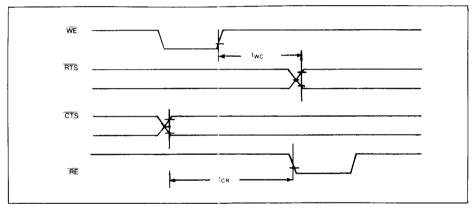

| twc              | Control Delay from Rising Edge of WRITE (RTS)                             |            | 200        | ns               |                             |

| tCR              | Control to READ Set-Up Time (CTS)                                         |            | 1          | tTXC             |                             |

| <sup>t</sup> MR  | Master Reset                                                              | 500        |            | ns               |                             |

FIGURE 7. WRITE TIMING

FIGURE 8. INTERFACE CONTROL TIMING

FIGURE 9. TRANSMITTER CLOCK AND DATA TIMING

FIGURE 10. RECEIVER CLOCK AND DATA TIMINGS

FIGURE 11. TRANSMITTER OUTPUT TIMINGS WITH RESPECT TO TRANSMIT CLOCK

FIGURE 12. RXRDY TIMING

FIGURE 13. TXRDY TIMING