# PERIPHERAL MODULES FOR BASIC COMPUTER

from an idea by J. Haudry

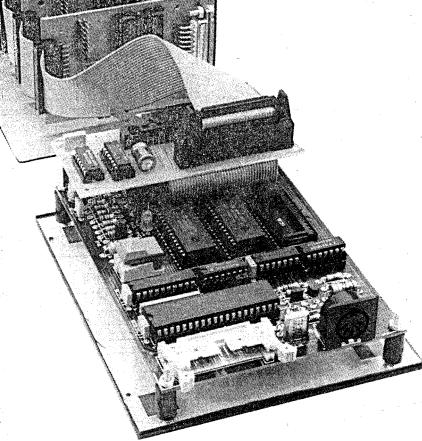

The 8052-based single-board process and control computer introduced in (1) is a system designed with hardware expansion in mind. This article describes two modular input/output boards that are indispensable when the BASIC computer is to control digital or analogue peripherals.

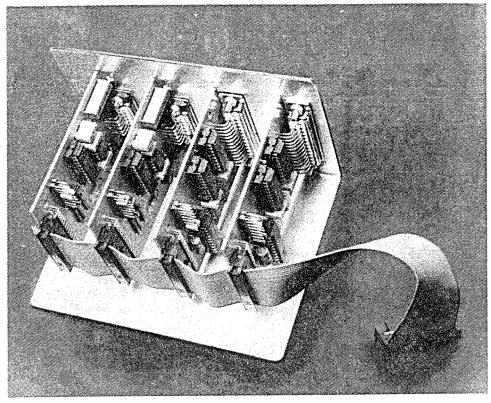

Peripheral modules for BASIC computer.

#### Chnical characteristics:

Modular I/O system comprises one address decoder/interface, and one or more input and/or output

Parallel mounting of up to eight digital I/O modules.

Analogue output module based on 10-bit DAC supplies accurate voltage for control applications.

Voltage span: 0 to 10.23 V, programmable in 10 mV steps:

Use of one or more analogue output modules restricts the maximum number of modules controlled by 1 address decoder/interface to 7.

Maximum of 2 address decoder/interface boards enables control of up to 16 digital I/O modules, or 14

Power digital outputs sink up to 500 mA at 50 V. Maximum total dissipation of output driver: 2.25 W Idiscipation is 0.5 W, for example, when 300 mA is supplied).

Just for those who do not know: the system described in reference (1) is a singleboard computer based on Intel's Type 8052AH-BASIC v1.1 microcontroller. As indicated by the type number, the computer can be programmed in BASIC. Programming is done with the aid of a dumb terminal (or a host computer running a terminal emulation program), and a bidirectional RS232 link to the BASIC computer. The system can run programs from an on-board EPROM, and is, therefore, ideal for small-scale process and control applications ('turnkey' systems). Interestingly, control software is written and debugged direct on the system, and loaded into EPROM by the CPU, i.e., without the need of an EPROM pro-

magazine.

The BASIC computer has been one of the most popular projects published over the last year or so in this magazine. Users have found it simple to build, program, and connect to existing equipment. The BASIC interpreter in the 8052AH-BASIC is relatively fast, and supports a number of extremely useful bit-manipulation commands. Machine code programming is also possible when the Intel reference guide is available. After our publishing of the 'bare bones' of the BASIC computer, many users have expressed a firm interest in input/output extensions for connection to the available bus. The modules described here are our answer to these requests. Readers may be interested to know that the modules are also compatible with a 8751-based autonomous input/output controller with RS232 interface, to be

described in a forthcoming issue of this

transiston kages have The AL figure of 5 dB, and 5 dB. The as a noise ed gain of 1 GHz of

Laser Road 💣 phone 01. utors out 1988 issue

ind manused prodof Arrow

istribution xiom will icts. In the rector of Lands of D's Sales hile Gree nager, and Executive,

Turnpikt • High Telephont

#### Functional description of the I/O modules

Two types of bus-connected module are described here:

- a bidirectional digital interface with 8 inputs and 8 buffered outputs;

- an analogue output module capable of supplying a highly accurate output voltage between 0 and +10.23 V, in steps of 10 mV.

Between the BASIC computer's bus and these modules sits a simple address decoder. The I/O modules are small units, and one address decoder allows parallel connection of up to 8 digital modules, or up to 7 modules when analogue and digital types are used simultaneously. The BASIC computer itself allows the connection of a maximum of two address decoders. The modular structure of the expanded BASIC computer is illustrated in the block diagram of Fig. 1. The address decoder provides a bus in the form of a flatcable, which runs from one I/O module to the next.

#### Address decoder for I/O modules

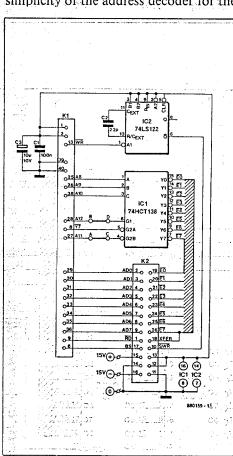

The circuit diagram of Fig. 2 shows the simplicity of the address decoder for the

WR BS(P1.0) BS 1 analogue **Y7** 8 inputs output 8052AH 8 buffered 0...10.23V **ADDRESS BASIC** <u> 8</u> outputs A9 DECODER COMPUTER 0 A10 -0 A11 E6 0 A12 O 880159 - 10

Fig. 1. The input/output system for the BASIC computer is a modular structure that give the user freedom of configuration. The I/O boards are connected direct to the databus of the microcontroller, but are addressed in the memory segment reserved for peripheral circuits

I/O modules. Monostable IC2 is used for timing one of the control signals for the 10-bit digital-to-analogue (D-A) con-

The presence of address lines All and A12 allows defining two address ranges. so that two decoders can be mounted in parallel, each with a different jumper configuration (A-D). Table 1 shows that each card occupies 256 addresses.

Address decoder IC1 supplies 8 enable signals, E0 to E7. The special use of E7 on the analogue output module will be reverted to, as well as the function of signal BS, which is supplied direct by the BASIC computer, and runs to the analogue output board(s) via the address decoder board.

short Wi

ontrolli

malogue

gidirec

output

the circ

emple u

Ci is ar

onnecte

compute

the risin

ggnal,  $\overline{V}$

held logi

when the

puter fal

umper

when th

ı digital

iumper

and jum

decoder

Circuit I

able line,

the read

xample,

on K3, an

lecoder

roller to

EC00 or

atabyte formed b

∛om Spr

Arlingto

<sup>Baductiv</sup>

goller.

Monostable IC2 changes the timing of  $\overline{WR}$  to provide a signal called  $\overline{SWR}$

Fig. 2. The interface shared by the I/O modules is composed of an address decoder that divides the available memory space for I/O in 8 blocks of 256 addresses, and a circuit that modifies the timing of the WR pulse to ensure correct loading of the D-A converter.

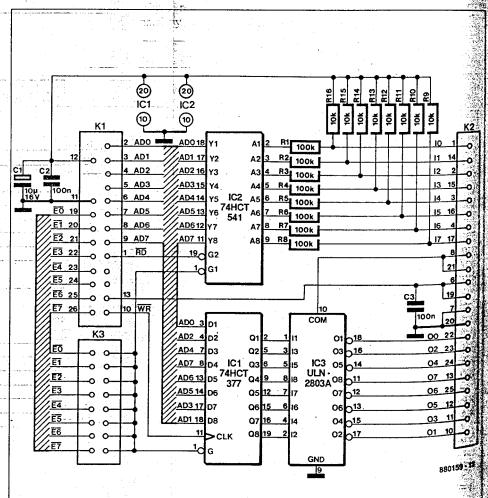

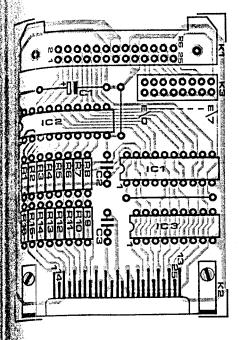

Fig. 3. Circuit diagram of the bidrectional digital interface. Up to 8 of these circuits can be controlled by a single and the circuits can be controlled by a single and the circuits can be controlled by a single and the circuits can be controlled by a single and the circuits can be controlled by a single and the circuits can be controlled by a single and the circuits can be controlled by a single and the circuits can be controlled by a single and the circuits can be controlled by a single and the circuits can be controlled by a single and the circuits can be controlled by a single and the circuits can be controlled by a single and the circuits can be controlled by a single and the circuits can be controlled by a single and the circuits can be controlled by a single and the circuits can be controlled by a single and the circuits can be controlled by a single and the circuits can be controlled by a single and the circuits can be controlled by a single and the circuits can be controlled by a single and the circuits can be controlled by a single and the circuits can be controlled by a single and the circuits can be controlled by a single and the circuits can be controlled by a single and the circuits can be controlled by a single and the circuits can be controlled by a single ca controlled by a single address decoder.

gort write or special write), needed for ing the D-A converter on the alog output module.

## gidirectional digital input/ sutput module

circuit diagram of this basically inple unit is given in Fig. 3. Circuit is an octal latch whose inputs are nnected to the databus of the BASIC imputer. Data is latched into IC1 on rising edge of the memory write nal,  $\overline{WR}$ , but only when input  $\overline{G}$  is logic low. This condition is satisfied hen the address supplied by the comsiter falls within the range preset by the mper on block K<sub>3</sub> (see Table 1.). that give when the processor writes a databyte to bus of the digital output, e.g., at address F600H, imper E6 should be installed on K3, ad jumpers BD and AC on the address scoder board (Fig. 2).

<del>)</del> - 10

circuits

8 enable

se of E7

ming of

d SWR

159 - 12

can be

e will be circuit IC2 is controlled by the same enction of the line,  $\overline{Ex}$ , as IC1, and in addition by ct by the read signal, RD, of the microconto the roller. As a further configuration address cample, jumper E4 should be installed on K3, and jumpers BC and AD on the fecoder board, to enable the microcongoller to read a databyte at address £000 on the digital I/O board. The tatabyte read by the selected card is firmed by the logic configuration of the

signals applied to inputs I0 to I7 on the 25-way D connector, K2. Note that the input lines have pull-up resistors, so that any non-connected input is read as a logic high level. The pull-up resistors allow the digital input to be connected direct to an existing open-collector or open-drain output.

**E6**

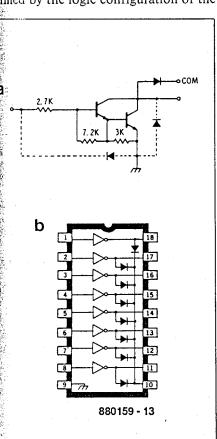

The Type ULN2803 in position IC3 is an 8-way inverting power buffer composed of high-voltage, high-current darlington transistor arrays. This IC enables the digital output to directly control a wide range of loads, such as relays, solenoids, stepper motors and LED displays. Figures 4a and 4b show the inter-

| enable<br>signal | wire links<br>BD and AC | wire links<br>BC and AD |

|------------------|-------------------------|-------------------------|

| EO               | F000F0FF                | E800E8FF                |

| E1               | F100F1FF                | E900E9FF                |

| E2               | F200F2FF                | EA00:EAFF               |

| E3               | F300F3FF                | EBOOEBFF                |

| E4               | F400F4FF                | ECOOECFF                |

| E5               | F500 F5FF               | EDOOEDFF                |

F600..

F700.

.F6FF

Address assignment of I/O modules.

EE00

EFOO.

EEFF

EFFF

Signal Y7 defines address range E000..., FFFF, split in two by A11 and A12.

All addresses in hexadecimal.

Table 1.

g. Internal diagram of the ULN2803 from prague. Each of the 8 surge-protected arlington transistors in this chip can switch inductive) loads of up to 500 mA.

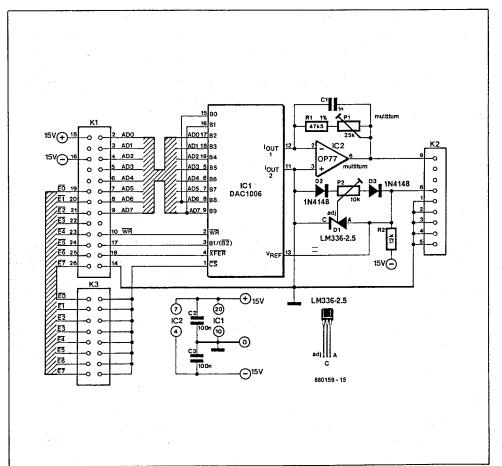

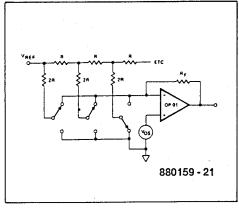

Fig. 5. The analogue output module is based around a 10-bit digital-to-analogue converter Type DAC1006 from National Semiconductor. The output voltage span is from 0 to 10.23 V in 10 mV steps.

nal structure of the ULN2803. Note that the buffers are of the inverting type, and that internal anti-surge diodes are provided to prevent damage to the opencollector output transistor when the current through the inductive load (relay coil) is interrupted. The anti-surge diodes are internally connected to a common rail, which is brought out to pin 10. This means that the supply voltage for the inductive loads controlled by the ULN2803 can be connected to pins 21 and 8 of K2.

### Analogue output module

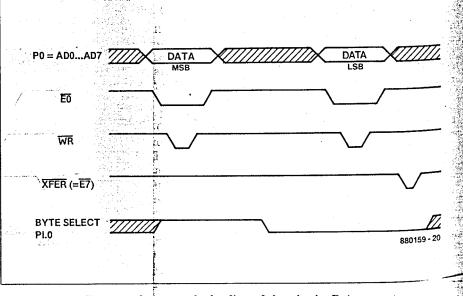

The heart of the D-A module shown in Fig. 5 is formed by IC, a Type DAC1006. This 10-bit DAC is remarkable for its excellent stability and capability to be controlled from an 8-bit bus. Loading of data (0 to 102310) is done in two successive operations, under

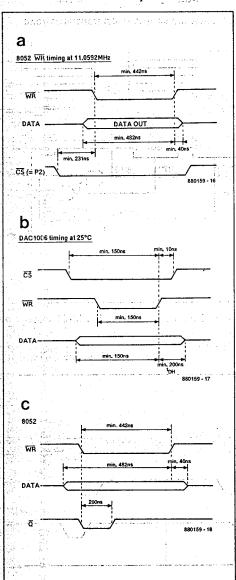

Fig. 6. For the DAC1006 to operate corectly, data should remain stable on the the databus for at least 200 ns following the rising edge of the WR pulse (Fig. 6b), which is not so on the databus of the 8052AH-BASIC (Fig. 6a;  $f_{CL}=11.0592 \text{ MHz}$ ). A monostable multivibrator is, therefore, required to shorten the WR pulse (Fig. 6c).

control of the logic level of the BS (byte select) signal applied to pin 3. This signal comes direct from the microcontroller 8052AH-BASIC via an output line of port P1. Users should decide for themselves which of these lines is to be used for providing signal BS.

The Type DAC1006 has pecularities which call for a rather special circuit configuration around it. Firstly, the DAC has a specific require-

ment as regards the duration of the poadi databyte. The timing diagrams of Fig. The se show that databytes are present on the pactor and pactor the Will provide the pactor. bus for only 40  $\mu$ s after the WR puls baded (Fig. 6a). The DAC1006, however, 15, 1011 Signature for at 15 and quires data to be present for at least 10 10-1 200 ns (Fig. 6b). This problem is solved by monostable IC<sub>2</sub> in the address decoder circuit (Fig. 2). Note that the 74LS122 used for this purpose is not available in the HCT version.

Fig. 7. The DAC1006 expects 10-bit, right-justified, data in a 16-bit dataword. Signal B. together with WR and CS, is needed to ensure that data from the 8-bit databus is sequentially latched into the device. A further signal, XFER, effects the transfer of the complete dataword from the latches to the internal conversion register.

Fig. 8. Timing diagram relevant to the loading of data in the D-A converter.

itis. U ge left ations. fightly DO to ossible is mul

rigina)

e load emaini 150 Fig Once tl the late the c conti mply ecoder pards ecoder output ne E7 agital lock tl anvers Figure 3 the sign inalogi EO, wh P1.0 of Smart

> a the = XF Sting The ex DAC10 hal co ₹nsate

for add

ne or eing u nsured

se cor ddress

rom he o hich C2. P tale re of 0P-77 ! onl ी 25 P S cou ava व coा €me

owev no. hile ाter <sup>S</sup>gita

onlig et ne

## nading the DAC

on the

Pulse

inal BS.

ientially

ataword

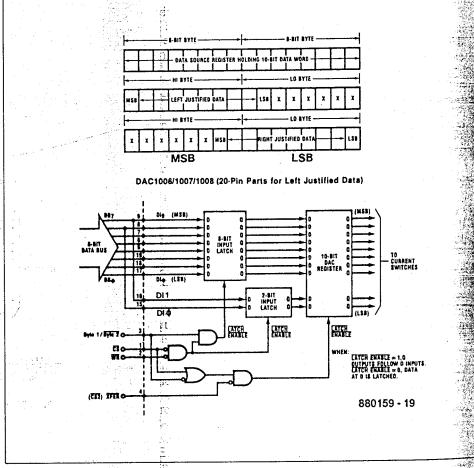

se nd peculiarity of the Type cloc has to do with the way it is ded with digital data. Figure 7 shows er, resignal BS allows the chip to latch it leas 10-bit dataword as 8, followed by 2, solver Unconventionally, the 10 databits address left-justified in 16 available bit lo-nat the ons. Fortunately, in spite of the is not htly unusual configuration of lines 0 to AD7, and B0 to B9, it is still sible to achieve right-justified data multiplication of the right-justified einal 10-bit data by 64. The first 8 bits loaded when BS is logic high, the 2 aining bits when BS is logic low (see Fig. 8).

e the 10-bit dataword is available in latches, it is ready to be transferred the conversion register. This operation controlled by signal XFER, which is aply Ex supplied by the address oder board. This explains why only 7 rds can be connected to the address coder when one or more analogue put cards are being used. In that case, E7 is not available for enabling a Itial I/O module because it serves to k the transfer of the databits to the nversion register in the DAC1006.

gure 8 shows the time relation between signals involved. As an example, the alogue output module is addressed by while BS is provided by port line 10 of the 8052AH-BASIC.

part ers may still be able to use E7 addressing an eighth card, even if e or more analogue output cards are ing used. This is possible provided it is sured that the contents of the latches correct the moment the 8th card is dressed, and that the databyte written the latch of the selected card by E7 XFER) is correct also (refer to the in Table 2).

external reference voltage for the C1006 is provided by D1, whose thercoefficient can be accurately comasated by preset P2.

## om current to voltage

output of IC<sub>1</sub> supplies a current ich is converted to voltage in opamp Preset P<sub>1</sub> allows defining the fullale value of the output voltage. The of a relatively expensive opamp Type 377, which achieves an offset voltage only 50 µs at an ambient temperature 25° C, may be questioned given the size of 'only' 10 mV.

could be argued that a more commonavailable opamp with an external offcompensation resistor would give the ne results as the OP-77. This is not so, wever, because the external compensaresistor would have a fixed value, e the output resistance of the conter chip changes with every new tal value loaded, due to the different figuration of the internal R-2R ladnetwork.

With reference to the simplified diagram of Fig. 9, the effect of this change on the static accuracy of the I-V converter can be expressed as the magnitude of the error voltage, calculated from

error voltage =  $V_{os}(1 + R_F/R_O)$

where Ro is a function of the digital value written to the DAC:

$R_0 \approx 10 \text{ k}\Omega$  for more than 4 logic high bits;

$R_0 \approx 30 \text{ k}\Omega$  for any single logic high

Therefore, the offset gain varies as follows:

code = 00111111111111:  $V_{err1} = V_{os}(1 + 10^4/10^4) = 2V_{os}$ .

code = 0100000000000:

$V_{err2} = V_{os}(1 + 10^4/3 \times 10^4) = \frac{4}{3}V_{os}$ .

The error difference between these values is <sup>2</sup>/<sub>3</sub> V<sub>os</sub>.

It will be evident from the above that the non-linearity of the output voltage is a function of the opamp's offset voltage. When this is low (OP-77), the maximum deviation is also low, athough still dependent of the digital value written to the DAC.

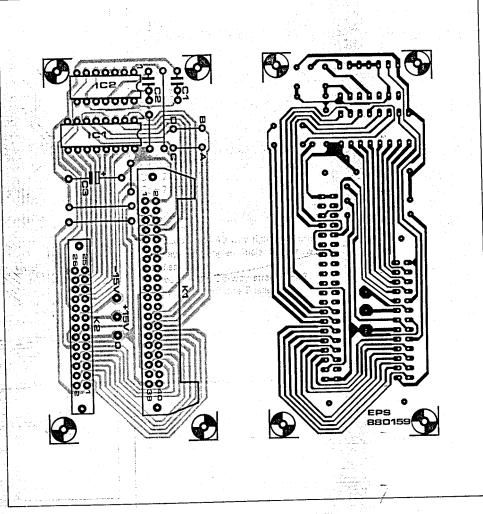

## Construction and alignment

The peripheral extension modules for the BASIC computer are three printed circuit boards (Figs. 10, 11 and 12) interconnected by a bus formed by flat ribbon cable. The layout of the boards is

such that the output connector, K2, can be fitted onto the equipment front panel, with the board mounted perpendicular to this at the inside. At the other end of the cards, a 26-way flatcable plugged into K1 runs from one card to another, connecting all of these to the bus card, which is mounted on the BASIC computer. The total length of the cable should not exceed about 30 cm to prevent digital interference on the databus.

The address decoder/interface card can be fitted direct on to the BASIC computer board, and is connected to it by a short length of flat ribbon cable. On the computer board, connect pin 7 of  $IC_3$  (address decoding signal  $\overline{Y7}$ ) to pin 8 of the 40-way connector (K2). It is also necessary to choose the Port 1 line to

Fig. 9. Variation in output resistance of the DAC as a function of the converted code gives rise to a variable offset current at the input of the opamp, which translates current to voltage, and so magnifies the offset voltage. Obviously, the offset voltage of the opamp itself should be as low as possible.

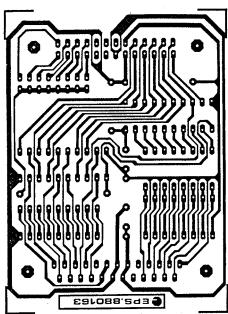

Fig. 10. Printed circuit board for the address decoder.

supply BS. The connection between pin 6 of K<sub>2</sub> and pin 19 of K<sub>1</sub> shows that we have opted for Port 1 line P1. Any other line is equally suitable, as long as the software for the I/O modules takes this into account.

If it is decided not to use the analogue oth output module, the last mentioned link can be omitted. Similarly, the ±15 Vocasion supply is not required then.

The modules are ready after being assigned a memory address by placing a jumper on K<sub>3</sub>.

There are only two, simple, adjustments to carry out on the analogue output board(s). First, correct the temperature coefficient of the LM336-2V5 by adjusting P<sub>2</sub> for a reference voltage of 2.490 V measured at pin 6 of the output connector, K<sub>2</sub>. Next, write 1000<sub>10</sub> to the DAC (10 mV/LSB) and set the full-scale output voltage to 10.00 V with the aid of

The I/O modules discussed have a relatively low current consumption, and are, therefore, conveniently powered from the existing supply for the BASIC computer. The analogue board draws about 10 mA, the digital board and the decoder each about 20 mA.

#### Final notes

Table 2.

The contents of the conversion register in the DAC1006 are not defined at power-on, so that the output voltage may not be nought then. When an XFER pulse is received by a DAC, all other DACs connected respond to this

simultaneously. This means that the contents of the latches should correspond to the desired output voltage, which into not be the case at power-on.

The analogue and digital ground in may only be connected on the address decoder board.

Examples of elementary command routines

Parts list

Capacitors: C1 = 100n

$C_2 = 22p$

$C3 = 10\mu$ ; 10 V

Semiconductors: IC1 = 74HCT138 IC2 = 74LS122

Miscellaneous:

handles.

K1 = double-row 40-way right-angled header 40-way right-angled male header with e

K<sub>2</sub> = double-row 26-way straight PCB header. PCB Type 880159 (see Readers Services page

ADDRESS DECODER BOARD

#### For analogue module:

REM output address (see K3) EO = OFOOOH100 REM dummy address (transfer) XF = 0F700H110 REM get byte to convert INPUT X 120 REM justify left  $\chi = \chi = 64$ 130 REM write byte PORT1 = 1140 REM i.e. MSB, and then XBY(E0) -= X/256150 REM ISB PORT1 = 0160 REM (only bits 6 et 7 XBY(EO) = X.AND.OFFH 170 REM clock 10-bit transfer XBY(XF) = 0REM end of loop 190 GOTO 120

#### For digital module:

10 E1 = 0F100H REM module address (see K3) 20 Y = X8Y(E1) REM read input byte from Y 30 XBY(E1) = 00F3H REM write byte F3

ader, er th eject

eader. : page).

the con-

pond to ch may

nd lines

address

:01)

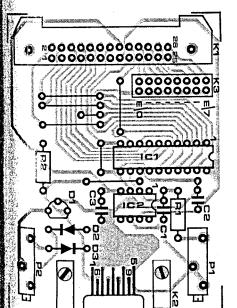

11. Printed circuit board for the digital I/O module.

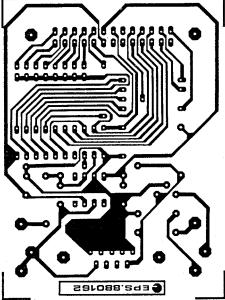

12. Printed circuit board for the analogue output module.

hen the logic outputs are used only for ving other digital circuits, the N2803 need not be fitted, and wire ks may be installed between the PCB anections intended for the inputs and uputs of the chip.

hally, lo not forget that E7 can not mally be used as a board selection thal because it is needed as XFER ared by the analogue output modules.

#### Reference:

(1) BASIC computer. Elektor Electronics November 1987, p. 24-31.

Parts list DIGITAL I/O BOARD

#### Resistors:

R1...Rs incl. = 100K R9...R16 incl. = 10K

#### Capacitors:

$C_1 = 10\mu$ ; 16 V C2;C3=100n

#### Semiconductors:

IC1 = 74HCT377 IC2 = 74HCT541 IC3=ULN2803A

#### Miscellaneous:

K1 = double-row 26-way right-angled header, or 26-way right-angled male header with eject

K2= 25-way D connector, male, with rightangled pins.

K3= double-row 16-way straight PCB header. 1 jumper for mounting on K3. PCB Type 880163 (see Readers Services page).

Parts list ANALOGUE OUTPUT BOARD

#### Resistors:

R1 = 47K5 1%  $R_2 = 12K$

P1 = 25K or 22K multiturn preset P2 = 10K multiturn preset

#### Capacitors:

$C_1 = 1n0$ C2;C3 = 100n

#### Semiconductors:

D1=LM336-2V5

D2:D3 = 1N4148

IC1 = DAC1006 (National Semiconductor)

IC2 = OP-77 (PMI)

#### Miscellaneous:

K1 = double-row 26-way right-angled header, or 26-way right-angled male header with eject handles.

K<sub>2</sub> = 9-way D connector, male, with right-angled pins.

K3 = double-row 16-way straight PCB header. 1 jumper for mounting on K3.

PCB Type 880162 (see Readers Services page).